Difference between revisions of "Config TIAO Universal JTAG Cable As A Buffered Xilinx Parallel Platform Cable III"

10 PCS, 10cm x 10cm, 2 layers prototype for $38.80 shipped!

| Line 18: | Line 18: | ||

In this tutorial, I am going to show you how to config it as a Xilinx Buffered Parallel Cable III to erase/read and program Xilinx CPLD. | In this tutorial, I am going to show you how to config it as a Xilinx Buffered Parallel Cable III to erase/read and program Xilinx CPLD. | ||

| + | |||

| + | <font color=red>This tutorial works for CPLDs operating on +3.3v voltage only</font> | ||

== Required Hardware == | == Required Hardware == | ||

| Line 85: | Line 87: | ||

* Now, you can use iMPACT to read/erase/write CPLDs. | * Now, you can use iMPACT to read/erase/write CPLDs. | ||

| − | You can | + | You can read [[Program Xilinx XC2C64A Or Similar Xilinx CPLD Using TIAO Universal JTAG Cable]] on how to program CPLD using our Universal Parallel JTAG board. |

Revision as of 19:11, 1 October 2011

Contents

Buy various JTAG cables for your Satellite Receiver, Cable Modem, Wireless Router, Standard Wiggler from http://www.easymg.com and http://www.diygadget.com

Overview

TIAO Universal Buffered Parallel JTAG Adapter is a multi-functional parallel JTAG adapter for hobbyists or engineers.

In this tutorial, I am going to show you how to config it as a Xilinx Buffered Parallel Cable III to erase/read and program Xilinx CPLD.

This tutorial works for CPLDs operating on +3.3v voltage only

Required Hardware

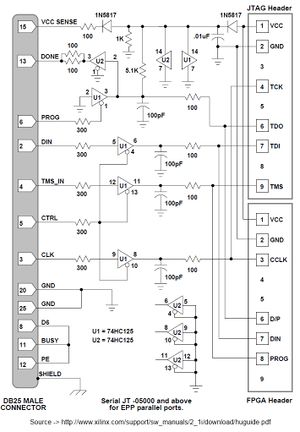

Xilinx Buffered Platform Cable III Schematic

This is the schematic of the official Xilinx Buffered Platform Cable III:

The key points of the schematic are as follows:

- PIN 2 of DB25 is TDI

- PIN 3 of DB25 is TCK

- PIN 4 of DB25 is TMS

- PIN 13 of DB25 is TDO

- PIN 8, 11 and 12 of DB25 are shorted (connected)

Thus, we can simulate the above schematic on TIAO Universal Buffered Parallel JTAG Adapter.

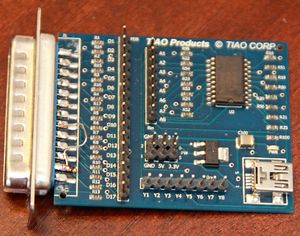

Xilinx Buffered Platform Cable III Connections on TIAO Universal Buffered Parallel JTAG Adapter

Basically, make the following connections:

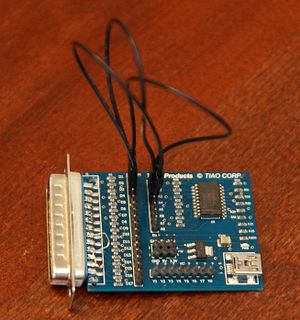

* Short DB25's pin 8, 11 and 12 * Use female to female jumper wire to connect D2, D3, D4, D13 to A1, A2, A3, Y8 on TIAO Universal JTAG adapter respectively. * Use female to female jumper wire to connect Y1, Y2, Y3, A8, GND, 3.3V to CPLD's TDI, TCK, TMS, TDO, GND and Vcc respectively.

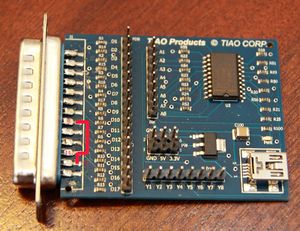

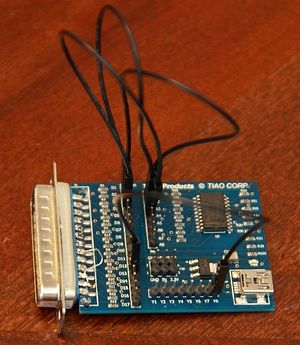

Short DB25's PIN 8, 11 and 12

In this step, you need to solder wires to make DB25's PIN 8, 11 and 12 connected.

I soldered them together with a leg of a resistor:

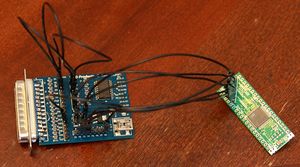

Connect the female to female wires

In this example, I use XC2C64A CoolRunner-II CPLD Dev Board (RGH) as the example:

Buy various JTAG cables for your Satellite Receiver, Cable Modem, Wireless Router, Standard Wiggler from http://www.easymg.com and http://www.diygadget.com

Connect the JTAG board to PC

- Connect the JTAG board and your PC with a USB A to Mini USB cable (most digital camera supplies this kind of cable)

- Plug the board to your PC's parallel port

- Run Xilinx iMPACT from lab tools, select Parallel Cable III in cable setup dialog

- Now, you can use iMPACT to read/erase/write CPLDs.

You can read Program Xilinx XC2C64A Or Similar Xilinx CPLD Using TIAO Universal JTAG Cable on how to program CPLD using our Universal Parallel JTAG board.

10 PCS, 10cm x 10cm, 2 layers prototype for $38.80 shipped!