Difference between revisions of "Config TIAO Universal JTAG Cable As A Buffered Xilinx Parallel Platform Cable III"

From TIAO's Wiki

10 PCS, 10cm x 10cm, 2 layers prototype for $38.80 shipped!

| Line 27: | Line 27: | ||

This is the schematic of the official Xilinx Buffered Platform Cable III: | This is the schematic of the official Xilinx Buffered Platform Cable III: | ||

| − | [[Image:Xilinx.platform.cable3.jpg|none]] | + | [[Image:Xilinx.platform.cable3.jpg|none|thumb]] |

The key points of the schematic are as follows: | The key points of the schematic are as follows: | ||

Revision as of 18:33, 1 October 2011

Buy various JTAG cables for your Satellite Receiver, Cable Modem, Wireless Router, Standard Wiggler from http://www.easymg.com and http://www.diygadget.com

Overview

TIAO Universal Buffered Parallel JTAG Adapter is a multi-functional parallel JTAG adapter for hobbyists or engineers.

In this tutorial, I am going to show you how to config it as a Xilinx Buffered Parallel Cable III to erase/read and program Xilinx CPLD.

Required Hardware

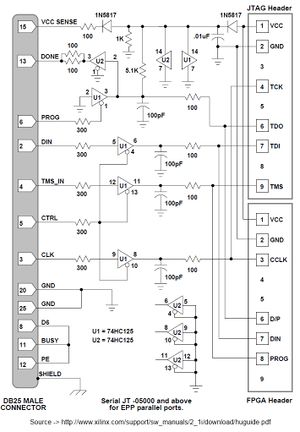

Xilinx Buffered Platform Cable III Schematic

This is the schematic of the official Xilinx Buffered Platform Cable III:

The key points of the schematic are as follows:

- PIN 2 of DB25 is TDI

- PIN 3 of DB25 is TCK

- PIN 4 of DB25 is TMS

- PIN 13 of DB25 is TDO

- PIN 8, 11 and 12 of DB25 are shorted (connected)

Buy various JTAG cables for your Satellite Receiver, Cable Modem, Wireless Router, Standard Wiggler from http://www.easymg.com and http://www.diygadget.com

10 PCS, 10cm x 10cm, 2 layers prototype for $38.80 shipped!